# Editor's Notes

## A & D-INSEPARABLE

You may ask: "Why is a journal with so much digital content still called "Analog Dialogue"?

The facile answer is that digital electronics is basically analog, since it deals in voltage and current; the analog values of signals establish their digital state. This argument gains some force when

you consider that a digital signal—which arrives buried in noise—must first be recovered as an analog signal before the digital information in it (which may in turn represent the results of an analog measurement) can be interpreted.

You can also look at it historically. Ever since our op amps were first used to process analog signals for data acquisition, Analog Devices, Inc., has been involved in some aspect of the digital processing of analog signals. Our involvement increased as we successively (and successfully) engaged in the manufacture of a/d and d/a converters, data-acquisition systems, microcomputer I/O interface boards, computer-based measurement and control systems—and now, components and subsystems for DSP. The "analog" aspect of our mission continues to be the real-world origin of the signals being processed—and real-world signals are predominantly analog. Conclusion: When real-world signals must be processed, Analog and digital are inseparable.

#### FATTENING UP THE DIALOGUE

If you're a typical reader, you've been reading Analog Dialogue for more than 2 years and are an E.E., working in measurement and control system design. When you read this magazine, you look first for applications articles but also have a strong interest in our new products. You don't think there's much room for improvement, but you do need more articles on signal conditioning, µP and µC interfacing, digital signal processing, op amps, and data-acquisition systems. The kinds of articles you need are mainly on practical matters (noise, grounding, etc.), but also include tutorials, applications ideas, applications by users (which you're always welcome to send to be considered), and cookbook examples. You're not much interested in technology or internal design of our products, unless it affects their application. You want more: more pages per issue, more issues per year, more material per article.

These are some of the things readers told us in a recent survey. We'd been eager to find out if our readers get what they want from Analog Dialogue and how we can do a better job. So we sent questionnaires with the last issue (16-3) to a random sampling of readers in the U.S. A sizeable proportion having been returned and analyzed, we've drawn this major conclusion: You have given us a mandate to increase the proportion of practical, tutorial, and idea-type articles. In order to do this without reducing the space devoted to technical information on new products (which you also want), we intend to gradually increase the total number of pages in each issue (which you also asked for). You asked for it? You've got it.

Dan Sheingold

### **THE AUTHORS**

A. Paul Brokaw (page 14) is a Division Fellow at Analog Devices Semiconductor. He has designed numerous successful ICs, including voltage references, ADCs, and amplifiers. His many activities include circuit design, new-product definition, contributions to the work of the Education-Support and Patent Committees, and men-

toring. He has numerous patents and publications and is active in IEEE. He has a B.S. in Physics from Oklahoma State University.

Moshe Gerstenhaber (page 14), an ADS Group Leader and designer of the AD630, co-authored "Analog Signal-Conditioning ICs Take Two Giant Steps;" it appeared in the last issue, with his biography and photo.

David J. Laing (page 20) is an Applications Engineer at the ADI Component Test Systems Division. A graduate of Northeastern University, he holds a BSEE (High Honors). Before joining ADI, he was employed at the Component Test Division of Gen-Rad, Inc., as a Senior Application Engineer on the GR 1732 Digital Test System.

Steve Miller (page 14) is an Applications Engineer at ADS. He holds a B.E. degree from the Thayer School of Engineering, where he also worked as a Research Assistant before joining Analog. Steve is an avid outdoorsman; his hobbies include running, cycling, canoeing, and cross-country skiing.

Jerry Neal (page 18) is a Regional Marketing Engineer at ADI's Computer Labs Division. A native of North Carolina, he attended N. C. State University. Prior to joining ADI, he invented, patented, and manufactured a soil moisture sensor; he has also worked for Hewlett Packard and Burroughs. He joined CLD in

1981, returning to N.C. with his wife, Linda, and their 4 children. They enjoy gardening and travel. (Continued on page 26)

# analog dialogue

2 Technology Way, P.O. Box 280, Norwood, Mass. 02062

Published by Analog Devices, Inc., and available at no charge to engineers and scientists who use or think about I.C. or discrete analog, conversion, data handling and display circuits and systems. Correspondence is welcome and should be addressed to Editor, *Analog Dialogue*, P.O. Box 280, Norwood, Massachusetts, U.S.A. 02062. Analog Devices, Inc., has representatives and sales offices throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-329-4700, TWX 710-394-6577 or 710-336-0562, Telex 924 491, or cable ANALOG NORWOODMASS.

# LOW-POWER DIGITAL SIGNAL-PROCESSING ICS

# Facilitate Filtering, FFT, Correlation, Averaging, and Much Else 8 X 8 and 16 X 16 Multipliers & Multiplier/Accumulators Dissipate <175 mW

by John Oxaal

The rapid growth of Digital Signal Processing (DSP) has led to a wealth of exciting new electronic end-products with a wide diversity of applications. The use of DSP has provided improved performance at lower cost in spectrum and analyzers, transmultiplexers, modems, medical imaging equipment, IC bonders, encryption devices, radars, and more. As the price of DSP circuits continues to fall—and especially in relation to what can be accomplished with them—and as engineers become more familiar with the techniques, we can look forward to a whole new generation of electronic equipment with significantly improved performance.

#### WHAT IS DSP?

Digital signal processing is not new. In its most general form, the term describes all of the operations that are done by and with digital logic circuitry and computers to condition or extract meaning from signals acquired in the real world. However, most computers process information sequentially, and they have difficulty performing timely and error-free number-crunching of large arrays of fast-changing data.

"DSP," in a more specialized meaning that has grown increasingly familiar—the sense in which we use it here—refers to techniques that enhance the computer's ability to process data rapidly and accurately, mainly by the introduction of hardware and firmware that provide the benefits of parallel processing. For some applications, a signal processor will be used in conjunction with a large mainframe to offload hairy computations and provide accelerated computing ability; at the other pole, the signal processor might constitute virtually the entire instrument, except for analog data-acquisition circuits, a certain amount of digital housekeeping furnished by a microprocessor, and—of course—user controls and display.

DSP, in an analogy to analog signal processing, consists of specialized techniques using high-performance circuits and programs that enable signals to be processed numerically at high speeds, often approaching real time, i.e., "analog speeds with digital accuracy."

Three of these techniques—filtering, correlation, and fast Fourier transformations (FFT)—comprise sixty or seventy percent of all current DSP practice. Another twenty percent involve matrix operations (multiplication or addition of two matrices) typically required for graphics and control. These techniques are briefly discussed in the following pages.

# FILTERING, CORRELATION, AND FFT

Digital filters are used for exactly the same purposes as analog filters; to pass signals in certain frequency bands and to attenuate signals in other frequency bands. Modern digital filtering is carried out by performing the successive multiplications and additions required to perform convolution in the time domain—corresponding to multiplication in the frequency domain.

To understand how a digital filter works, remember that, in the

frequency domain, the spectrum of the input signal is multiplied by the frequency response function of the filter circuit to produce an output signal having a predetermined set of frequency components. You may recall that this multiplication in the frequency domain is equivalent to the convolution of two signals in the time domain, i.e., integration of the product of the folded input time function,  $f(\tau-t)$ , and an indicial response function of  $\tau$ . An analog filter circuit automatically performs the convolution implied by its physical circuit architecture and coefficients to provide the (real) time-domain response, but manually computed response predictions are easier to perform in the frequency domain, using the classical continuous calculus.

| INTHISISSUE                                                                 |

|-----------------------------------------------------------------------------|

| Volume 17, Number 1, 1982, 28 Pages                                         |

| Editor's Notes, Authors                                                     |

| Low-Power Digital Signal-Processing ICs                                     |

| Shielding and Guarding                                                      |

| Fast, Flexible Switched Dual-Input IC Op Amp & Comparator for               |

| Modulation, Demodulation, Synchronous Detection, etc                        |

| Level-Independent Automatic Gain Control with IC LOGDACTM 16                |

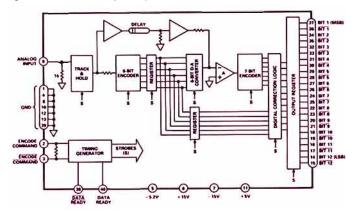

| 12-Bit, 10-MIlz Analog-to-Digital Converter                                 |

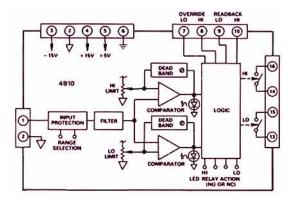

| Alarm Limit Subsystem Is Modular and Rugged                                 |

| Test MOS and Bipolar SSI & MSI Digital ICs with 1.TS-2000 Test Systems . 20 |

| Understanding the MACSYM 150/350 Software                                   |

| New-Product Briefs:                                                         |

| Ultrafast 8-Bit Monolithic DAC Settles in 5 ns (AD9768SD) 24                |

| High-Speed Single and Dual IC Sampling Comparators                          |

| (AD9685 & AD9687)                                                           |

| Video-Speed 100-mA Op Amp Settles to 0.1% in 80 ns (HOS-060) 24             |

| MULTIBUS-Comparible 12-Bit Analog I/O Boards                                |

| (RTI-711, -724 & -732)                                                      |

| 16-Bit Synchro/Resolver-Digital Converters (SDC1721, RDC1721) 25            |

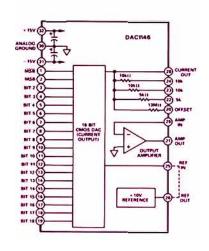

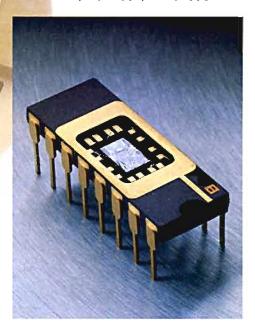

| 18-Bit DAC Has Low Cost, Linearity to 0,00076% (DAC1146) 25                 |

| Worth Reading (Application Notes, Brochures, Reprints, Test-Program         |

| Library)                                                                    |

| More Authors                                                                |

| Potpourri                                                                   |

| Advertisement                                                               |

Analog Dialogue 17-1 1983

Digital signal processing, however, makes it possible to perform large numbers of accurate incremental calculations in a short time. In digital signal processing, difference calculus replaces differential calculus, and time-response of the filter can be calculated directly by convolution. The input signal is already available in the form of a sampled time function in suitable increments (for all values of  $\tau$ ), the indicial response function for each time increment can be computed initially and stored in memory, and integration is replaced by summation. With today's components, multiplication (16 bits  $\times$  16 bits) and addition can be performed rapidly (e.g., at 5-MHz rates), repeatedly, at low cost, and with low dissipation (less than 175 mW) and no drift.

A typical digital filtering process is illustrated by (1):

$$Y(n) = \sum_{m=0}^{n-1} H(m) X(n-m)$$

(1)

Each output sample, Y(n), is obtained by multiplying m input samples, X(n-m), by m coefficients, H(m), and summing the results.

The filter coefficients, H(m), are weighted in the time domain so that, when transformed to the frequency domain, they describe the desired filter response. An ideal brick-wall low-pass filter, for example, is a square-wave in the frequency domain; thus the time-domain representation of its amplitude would be a  $(\sin x)/x$  function of infinite duration. The H(m) would then be weighted according to a realizable approximation to that function. The convolving of the X(n-m) with the H(m) through equation 1 has the effect of multiplying the spectrum of the X(n-m) with that of the H(m). Since the frequency spectrum of the H(m) approximates the desired filter response, the Y(n) represent the correct values of time response appropriate to the filter characteristic and input waveshape.

Correlation is used to compare two signals, one of which is translated in time by a range of time delays. Auto-correlation compares a signal with delayed versions of the same signal; cross-correlation compares two different signals over a range of delay times. An algorithm for the digital implementation is

$$R(N) = \sum_{m=0}^{n-1} X(m) Y(m+N) \quad 0 < N \le n-1$$

(2)

The degree to which X(m), the values of X at different times, m, are the same as the values of Y, Y(m+N), for a given delay time, N, determines the magnitude of R(N)—and thus the correlation between the two signals at time N- and provides a correlation function over all N, in the range 0 to n-1.

As in the case of filtering, the algorithm employs a large number of successive multiplications and additions and is thus well suited for computation by DSP.

The Discrete Fourier Transform, very similar to the function performed by the more-efficient fast Fourier transform (FFT), is simply a sampled version of the Fourier transform where:

$$F(k) = \sum_{m=0}^{N-1} f(m) e^{-j2\pi mk/N}$$

(3)

The transform variable, k, corresponds to frequency, m to time, and N is a normalizing factor. The Fourier components, F(k), of the Discrete Fourier Transform are equivalent to the H(w) of the continuous Fourier Transform shown below.

$$H(w) = \int_{-\infty}^{+\infty} h(t) e^{-jwt} dt$$

(4)

The fast Fourier transform performs the same function as the discrete Fourier transform but is much more computationally efficient.

### MATRICES

Modern graphics and control systems make extensive use of matrix multiplications. For example, to reduce the scale of an object on a graphics screen one must multiply the address of every point on the object by a number less than 1. To scale the point P(X,Y,Z)

$$P'(X, Y, Z) = P(X, Y, Z) \cdot S(S_x, S_y, S_z)$$

$$= [X, Y, Z, 1] \cdot \begin{vmatrix} S_{x} & 0 & 0 & 0 \\ 0 & S_{y} & 0 & 0 \\ 0 & 0 & S_{z} & 0 \\ 0 & 0 & 0 & 1 \end{vmatrix}$$

$$P'(X, Y, Z) = [X \cdot S_x, Y \cdot S_y, Z \cdot S_z, 1]$$

(5)

Similar operations abound in the control and graphics industries.

Note that each DSP technique requires multipliers, to multiply two variables, and/or multiplier-accumulators, to perform the multiplication and accumulate the sum of the products. Since the fastest microprocessors require about 5 µs to perform a multiplication, their throughput rate—while performing the many repetitive operations called for by DSP—is quite slow. To enhance the speed of computation, dedicated peripheral devices operating at around 150ns per multiplication are required to obtain the throughput necessary for most of today's real-world signals. For this reason, multipliers are today the fundamental building block of DSP. Future unit device-functions for DSP will contain, in addition to multiplication, the on-chip memory, sequencing, and programming hooks necessary to perform the complete DSP algorithms shown above at considerably lower cost for comparable operations.

#### WHY USE DSP?

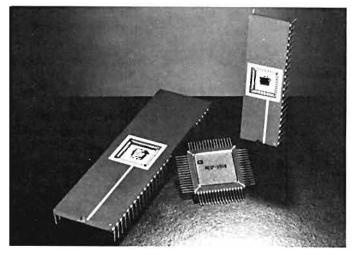

DSP is used to perform many of the same basic functions as analog signal processing. For example, analog filters and digital filters both pass signals in certain bands and attenuate signals outside that band. Digital signal processing, due to its higher cost, is used only when very high performance is required. For example, the 90th order FIR (finite impulse-response) filter transfer function shown in Figure 1 has a rolloff of 80dB/octave and can operate on 50kHz input signals. The phase response in the passband is linear.

The equivalent 13-pole analog filter would require at least seven op amps, many capacitors and resistors, and a long time to design. Moreover, the resulting filter would not be stable over time, temperature and power supply fluctuations; and to make it adjustable would be a near-impossible task.

Since the response of a digitally implemented filter is both stable and calculable—hence predictable—DSP is ideal for use in processors where stable implementation of very sharp rolloffs is required

Figure 1. Normalized transfer function of 90-tap FiR filter having 0.024% passband ripple and 80dB/octave attenuation.

(e.g., spectrum analyzers and transmultiplexers) and/or where it is necessary to dynamically alter the transfer function of the system (e.g., adaptive filtering in the equalizer of a modem).

The advantages of digital signal processing in product development are substantial: prototype changes are commonly just software changes (high flexibility), and software simulation of the system will reflect the exact system performance. Simulation of analog systems cannot duplicate this precise correspondence. These advantages make DSP desirable in many applications where predictable performance is an inescapable requirement.

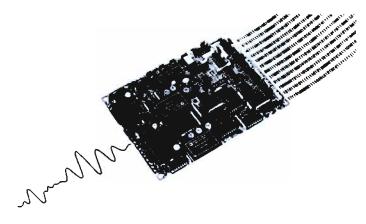

# WHY IS ANALOG DEVICES BUILDING DSP CIRCUITS?

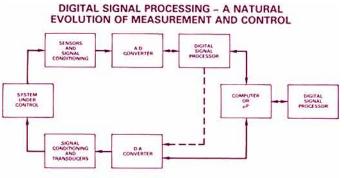

The declared business of Analog Devices is to develop components, subsystems, and systems for real-world signal processing, which includes measurement and control. The typical elements of a measurement-and-control loop, and the opportunities for digital signal processing, are shown in Figure 2. It is easy to see that DSP can ofter powerful enhancements to this loop. For example, digital filtering could be used for noise reduction before the signal is processed, stored, or handled by the computer; and, for complex computations, an array processor could be used to provide accelerated computer performance.

Figure 2. Signal processing in measurement and control.

In digital image-processing, the input to the DSP block would be video signals, and the output of the digital signal processor would drive a DAC that provides the intensity signal, as well as perform-

ing other functions, such as synchronization, etc. (We are already a major producer of video ADCs and DACs for those systems.)

Thus, DSP theory is a good fit to much of the signal handling in measurement and control, and video displays, which involve real-time signal processing. Also, our circuit-development and semiconductor-processing competences make it feasible to produce IC products to implement DSP theory at low cost and with low power consumption. Since DSP has such high potential applicability to our present measurement and control business, and DSP can now be economically implemented, and because our entry into the market as a competitor will clearly benefit all users of DSP—present and future—Analog Devices is making a strong commitment to the development, manufacture, and sale of products for DSP.

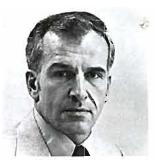

# LOW POWER MULTIPLIERS AND MACS

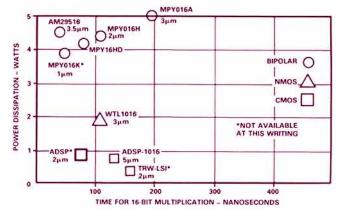

As the first DSP fruits of our ten years of experience with CMOS, we have developed and manufactured the industry's first low-power CMOS multipliers and multiplier-accumulators. Four devices, pin-compatible second sources to industry-standard 8 × 8 and 16 × 16-bit multipliers and multiplier/accumulators, offer speed comparable to bipolar and NMOS devices but dissipate only 1/20th as much power. Thus, as Figure 3 shows, we have minimized the designer's necessity for a speed/power tradeoff.

Figure 3. Dissipation vs. multiplying time for typical  $16 \times 16$  multipliers.

The ADSP-1080\* is an 8  $\times$  8-bit multiplier with 100mW maximum power dissipation and 85-ns typical† multiplication time (compare: 1.65W and 65ns for the TDC-8HJ). The ADSP-1016\* is a 16  $\times$  16-bit multiplier with 150mW maximum power dissipation and 130-ns typical cycle time (cf. 4.5W and 100ns for the MPY-16J). Prices for commercial-grade ADSP's in ceramic DIPS are \$45 (8  $\times$  8) and \$147 (16  $\times$  16) in 100s.

A multiplier/accumulator that is pin-compatible with the TDC1008J, the  $8\times8$ -bit ADSP-1008° offers typical cycle time of 100 ns with 100-mW maximum power dissipation (vs. 70 ns and 2.15W). The ADSP-1010,\* a  $16\times16$  device that is pin-compatible with the TDC1010J multiplier/accumulator, specifies typical cycle time of 150 ns and maximum power dissipation of 175mW (vs. 120 ns and 5.5 W). Power dissipation specifications are guaranteed over the ADSPs' respective ambient temperature ranges. Prices for commercial grades in ceramic are \$65 (8  $\times$  8) and \$198 (16  $\times$  16) in 100s.

Analog Dialogue 17-1 1983

<sup>\*</sup> For technical data use the reply card.

<sup>†&#</sup>x27;Typical' means maximum multiplication time at 25°C.

Although slower at 25°C, the CMOS ADSPs' speed—temperature coefficient of 0.3% per °C (typical) results in speeds comparable to those of the older bipolar devices at +125°C. For example, at +125°C, 16 × 16 multiplication typically requires 175ns for the ADSP-1016, compared to 185ns for the MPY-16HJ. Furthermore, unlike devices with high dissipation, the cool-running CMOS ADSPs are specified at ambient still-air—rather than case—temperature. All models are available for both commercial and military temperature ranges, and the latter are available with processing to MIL-STD-883B; low power-dissipation also allows the devices to be offered in leaded chip carriers.

The ADSP devices are fabricated in a proprietary oxide-isolated bulk CMOS process employing an easily attained 5-µm feature size. High speed is achieved through such time-saving circuit techniques as: feedforward carry circuits, modified Booth algorithms and conditional-sum adders.

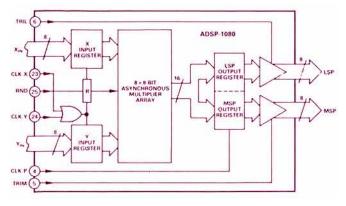

Figure 4 is a block diagram of the  $8 \times 8$  ADSP-1080 CMOS multiplier. It consists of an asynchronous multiplier array, a pair of 8-bit input registers, a pair of 8-bit output registers, and control logic. The hard-wired multiplier array performs long multiplication, radix 2, much as you would do it with pencil and paper—but with additional tricks, mentioned above, to simplify and quicken the process. In order to avoid loss of accuracy in later computations due to roundoff error, all 16 output digits are preserved (multiplication can double the number of bits, for example,  $(11 \times 11)_2 = 1001_2$ ).

Figure 4. Block diagram of the  $8 \times 8$  ADSP-1080 CMOS multiplier.

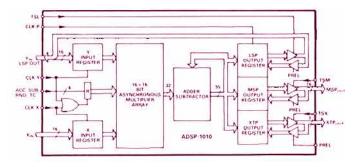

Figure 5 is a block diagram of the  $16 \times 16$  ADSP-1010 multiplier-accumulator. Like a  $16 \times 16$  ordinary multiplier, it has an asynchronous multiplier with a 32-bit output, two input registers, two product registers to accommodate the full product, and control logic. It also has an adder-subtractor to accumulate products and

Figure 5. Block diagram of the 16 × 16 ADSP-1010 multiplier/accumulator.

a 3-bit extended-product output register to avoid overflow when products are summed. Its least-significant-product output register shares a 16-bit bus with the Y-input register.

#### **APPLICATIONS**

In digital filters, a succession of samples of the signal are multiplied by programmed constants and summed. If the samples include samples of the output, then the filter is recursive, and the output may continue to respond long after the input has reached equilibrium. This is an infinite impulse response filter. However, if the output depends only on the input samples, the output will always reach equilibrium at a finite time after the input has reached equilibrium; this is a finite-response (FIR) filter. Design techniques for the two types of filter differ, but as noted earlier, they involve multiplication and addition.

We've prepared a series of S articles comprising cookbook designs applying DSP to FIR (finite impulse-response) filtering, IIR (infinite impulse-response) filtering, digital heterodyning and decimation filtering, temporal averaging of images and waveforms, and implementation of modern control theory. These articles, all of them "meaty," were committed for publication in the trade press, started with EDN's March 3, 1983 issue. If you would like reprints of the articles (when available), use the reply card, specifying those topics of specific interest to you.

We have included here a relatively simple example in which digital signal processing is applied to a piecewise-linear-approximation interpolation method that substantially reduces the memory required to implement table lookups.

# Piecewise-Linear Approximation

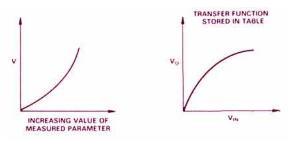

Often one has a need to perform a nonlinear transformation on a signal or data. For example, the calibration characteristics of a transducer can be nonlinear. The nonlinearity may be corrected for by adding a correction signal, multiplying by a correction factor, or mapping the inverse of the nonlinear function, as shown in Figure 6. To determine the inverse transformation over all input values, some form of storage of the function by analog or digital means is necessary.

(a) Nonlinear response. (b) Inverse function.

(c) Resulting overall linear function obtained by mapping (b) onto (a).

Figure 6. Nonlinearity correction by function fitting.

In analog circuitry, piecewise-linear function fitting is a time-honored approach to the generation of arbitrary nonlinear relationships between two variables, since it was first used for simulation of nonlinearities in analog computing by G. A. Philbrick in the 40s. Although easy to implement for simple relationships and accuracies in the 0.2% to 5% range, it becomes unwieldy—if not impossible—when embodying relationships having many changes of slope and requiring precision to 0.01% or better.

In digital systems, where high speed of response is required, mapping the inverse function using a lookup table is an effective approach. However, large amounts of memory may be required if the highest resolutions and accuracies are to be obtained, especially if more than one function is involved. The most efficient approach in such circumstances may be to store a reasonable number of data points in memory for each function and perform fast interpolations with firmware.

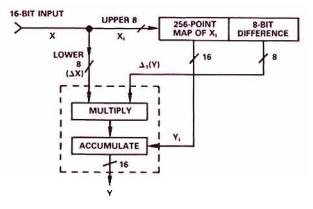

Figure 7 shows a scheme employing piecewise-linear approximation. An input 16-bit word, X, is divided into two 8-bit bytes,  $X_i$  and  $\Delta X$ , where i is any integer between 0 and 255, and  $\Delta X$  lies between 0 and (1-255/256), in increments of  $\frac{1}{256}$ .

Figure 7. Configuration to obtain 16-bit function-fitting with 512 memory points, using piecewise-linear interpolation.

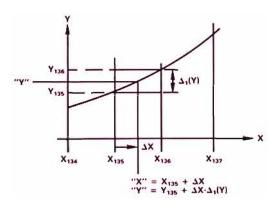

$X_i$ , the number corresponding to the upper 8 bits of X, serves as an address to access two items of data stored in memory,  $Y_i$ , the value of Y corresponding to  $X_i$ , with 16-bit resolution, and the first difference,  $\Delta_1(Y)$ , the change in Y corresponding to a 1-bit increase in  $X_i$ . The relationships between these quantities are shown in Figure 8.

Figure 8. Graphical interpretation of interpolation.

The lookup table contains the value of the function at a given point and its first difference (Figure 9)

If you wish to interpolate linearly between the points,  $X_i$ , the new value of Y is given by

$$Y = Y_i + \Delta X \cdot \Delta_1(Y) \tag{6}$$

As Figure 7 shows,  $\Delta X$ , the lower 8 bits of X, and  $\Delta_1(Y)$ , from

| Xi                                   | Yi                                   | $\Delta_1(Y)$                      |

|--------------------------------------|--------------------------------------|------------------------------------|

| X <sub>0</sub><br>X <sub>1</sub>     | Yo                                   | Y1-Y0                              |

| X <sub>1</sub>                       | Υ,                                   | $Y_1-Y_0$<br>$Y_2-Y_1$             |

| :                                    | :                                    |                                    |

| :                                    | :                                    |                                    |

| •                                    | :                                    | :                                  |

| : 1                                  | •                                    | •                                  |

| •                                    | :                                    |                                    |

| X <sub>254</sub>                     | Y <sub>254</sub>                     | Y <sub>255</sub> -Y <sub>254</sub> |

| X <sub>254</sub><br>X <sub>255</sub> | Y <sub>254</sub><br>Y <sub>255</sub> |                                    |

Figure 9. Lookup table.

memory, are strobed into the lower 8 bits of X and Y, multiplied, and added to (or subtracted from) Y<sub>i</sub>, which was preloaded from memory into the lowest 8 bits of the MSP register and the highest 8 bits of the LSP register, in an ADSP-1010 multiplier/accumulator, which, in effect, executes (6). An 8 × 8 multiplier, ADSP-1080, could be used, if sufficient time is available to use the microprocessor's accumulator to perform the addition.

Other means of interpolation are also available, to obtain a closer fit, or to perform the fit using a smaller number of memory points. For example, a quadratic approximation could be used, employing an additional multiplier or multiplier/accumulator, or—if time permits—a second multiplication with the same multiplier, using the system microprocessor for the housekeeping and addition.

## FOR FURTHER READING

In addition to the series of articles mentioned on page 6, available from ADI, the following publications may be helpful to the reader seeking more information about digital signal processing. These publications are not available from Analog Devices.

R. W. Hamming, *Digital Filters*, Second Edition (Englewood Cliffs, New Jersey: Prentice-Hall, 1983).

J. H. McClellan, T. W. Parks, and L. R. Rabiner, "A Computer Program for Designing Optimum FIR Linear-Phase Digital Filters," *IEEE Transactions on Audio and Electroacoustics*, Vol. AU-21, No. 8, December, 1973.

Alan V. Oppenheim and Ronald W. Schafer, Digital Signal Processing (Englewood Cliffs, New Jersey: Prentice-Hall, 1975).

L. R. Rabiner, "Practical Design Rules for Optimum Finite-Impulse Response Low-Pass Digital Filters," *The Bell System Technical Journal*, Vol. 52, No. 6, July-August, 1973.

Lawrence R. Rabiner and Bernard Gold, Theory and Application of Digital Signal Processing (Englewood Cliffs, New Jersey: Prentice-Hall, 1975).

Ken Steiglitz, "Computer-Aided Design of Recursive Digital Filters," *IEEE Transactions on Audio and Electroacoustics* 18, (No. 2, June, 1970): pp. 123-129.

Ken Steiglitz, "The Equivalence of Digital and Analog Signal Processing," *IEEE Transactions on Information and Control* 8, (No. 5, October, 1965): pp. 455-467.

<sup>1</sup>Sheingold, ed. Nonlinear Circuits Handbook, 1974. Norwood: Analog Devices, Inc. pp. 43-44, 52-55, and 93-97.

Analog Dialogue 17-1 1983

# SHIELDING AND GUARDING

# How to Exclude Interference-Type Noise What to Do and Why to Do It—A Rational Approach

by Alan Rich

This is the second of two articles dealing with interference noise. In the last issue of Analog Dialogue (Vol. 16, No. 3, pp. 16-19), we discussed the nature of interference, described the relationship between sources, coupling channels, and receivers, and considered means of combatting interference in systems by reducing or eliminating one of those three elements.

One of the means of reducing noise coupling is shielding. Our purpose in this article is to describe the correct uses of shielding to reduce noise. The major topics we will discuss include noise due to capacitive coupling, noise due to magnetic coupling, and driven shields and guards. A set of guidelines will be included, with do's and don'ts.

From the outset, it should be noted that shielding problems are always rational and do not involve the occult; but they are not always straightforward. Each problem must be analyzed carefully. It is important first to identify the noise source, the receiver, and the coupling medium. Improper shielding and grounding, based on faulty identification of any of these elements, may only make matters worse or create a new problem.

You can think of shielding as serving two purposes. First, shielding can be used to confine noise to a small region; this will prevent noise from extending its reach and getting into a nearby critical circuit. However, the problem with such shields is that noise captured by the shield can still cause problems if the return path the noise takes is not carefully planned and implemented by understanding of the ground system and making the connections correctly.

Second, if noise is present in a system, shields can be placed around critical circuits to prevent the noise from getting into sensitive portions of the circuits. These shields can consist of metal boxes around circuit regions or cables with shields around the center conductors. Again, where and how the shields are connected is important.

#### **CAPACITIVELY COUPLED NOISE**

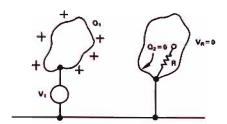

If the noise results from an electric field, a shield works because a charge,  $Q_2$ , resulting from an external potential,  $V_1$ , cannot exist on the interior of a closed conducting surface (Figure 1).

Figure 1. Charge  $\Omega_1$  cannot create charge inside a closed metal shell.

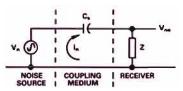

Coupling by mutual, or stray, capacitance can be modeled by the circuit of Figure 2. Here,  $V_n$  is a noise source (switching transistor,

TTL gate, etc.),  $C_a$  is the stray capacitance, Z is the impedance of a receiver (for example, a bypass resistor connected between the input of a high-gain amplifier and ground), and  $V_{no}$  is the output noise developed across Z.

Figure 2. Equivalent circuit of capacitive coupling between a source and a nearby impedance.

A noise current,  $i_n = V_n/(Z + Z_{Cs})$ , will result, producing a noise voltage,  $V_{no} = V_n/(1 + Z_{Cs}/Z)$ . For example, if  $C_s = 2.5$  pF,  $Z = 10k\Omega$  (resistive), and  $V_n = 100$ mV at 1.3 MHz, the output noise will be 20 mV (0.2% of 10V, i.e., 8 LSBs of 12 bits).

It is important to recognize the effect that very small amounts of stray capacitance will have on sensitive circuits. This becomes increasingly critical as systems are being designed to combine circuits operating at lower power (implying higher impedance levels), higher speed (implying lower nodal stray capacitance, faster edges, and higher frequencies), and higher resolution (much less output noise permitted).

When a shield is added, the change to the situation of Figure 2 is exemplified by the circuit model of Figure 3. With the assumption that the shield has zero impedance, the noise current in loop A-B-D-A will be  $V_n/Z_{C_k1}$ , but the noise current in loop D-B-C-D will be zero, since there is no driving source in that loop. And, since no current flows, there will be no voltage developed across Z. The sensitive circuit has thus been shielded from the noise source,  $V_n$ .

Figure 3. Equivalent circuit of the situation of Figure 2, with a shield interposed between the source and the impedance.

#### Guidelines for Applying Electrostatic Shields

- •An electrostatic shield, to be effective, should be connected to the reference potential of any circuitry contained within the shield. If the signal is earthed or grounded (i.e., connected to a metal chassis or frame, and/or to earth), the shield must be earthed or grounded. But grounding the shield is useless if the signal is not grounded.

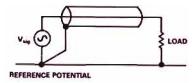

- •The shield conductor of a shielded cable should be connected to the reference potential at the signal-reference node (Figure 4).

- •If the shield is split into sections, as might occur if connectors are used, the shield for each segment must be ried to those for the

Figure 4. Grounding a cable shield.

adjoining segments, and ultimately connected (only) to the signal-reference node (Figure 5).

Figure 5. Shields must be interconnected if interrupted.

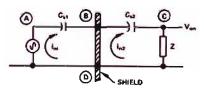

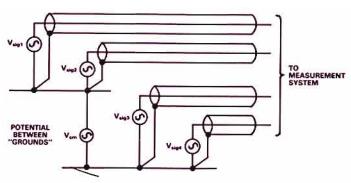

•The number of separate shields required in a system is equal to the number of independent signals that are being measured. Each signal should have its own shield, with no connections to other shields in the system, unless they share a common reference potential (signal "ground"). If there is more than one signal ground (Figure 6), each shield should be connected to its own reference potential.

Figure 6. Each signal should have its own shield connected to its own reference potential.

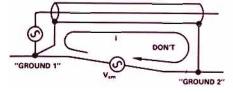

•Don't connect both ends of the shield to "ground". The potential difference between the two "grounds" will cause a shield current to flow (Figure 7). The shield current will induce a noise voltage into the center conductor via magnetic coupling. An example of this can be found in Part 1 of this series, Analog Dialogue 16-3, page 18, Figure 10.

Figure 7. Don't connect the shield to ground at more than one point.

- •Don't allow shield current to exist (except as noted later in this article). The shield current will induce a voltage in the center conductor.

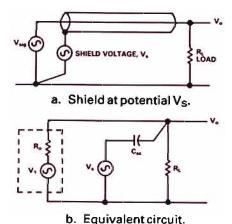

- •Don't allow the shield to be at a voltage with respect to the reference potential (except in the case of a guard shield, to be described). The shield voltage will couple capacitively to the center conductor (or conductors in a multiple-conductor shield). With a noise voltage, V<sub>s</sub>, on the shield, the situation is as shown in Figure 8.

Figure 8. Don't permit the shield to be at a potential with respect to the signal.

The fraction of V, appearing at the output will be

$$V_{o} = \frac{V_{s}}{\sqrt{1 + \frac{1}{(2\pi f R_{cq} C_{sc})^{2}}}}$$

(1)

where  $V_1$  is the open-circuit signal voltage,  $R_o$  is the signal's source impedance,  $C_{sc}$  is the cable's shield-to-conductor capacitance, and  $R_{eq}$  is the equivalent parallel resistance of  $R_o$  and  $R_L$ . For example, if  $V_s = 1V$  at 1.5 MHz,  $C_{sc} = 200$ pF (10 feet of cable),  $R_o = 1000$  ohms, and  $R_L = 10$ k $\Omega$ , the output noise voltage will be 0.86 volts.

This is an often-ignored guideline; serious noise problems can be created by inadvertently applying undesired potentials to the shield.

•Know by careful study how the noise current that has been captured by the shield returns to "ground." An improperly returned shield can cause shield voltages, can couple into other circuits, or couple into other shields. The shield return should be as short as possible to minimize inductance.

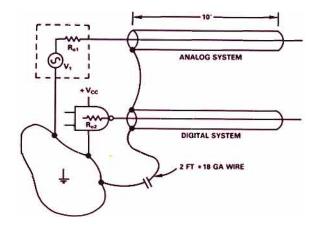

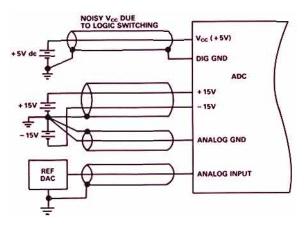

Here is an example that illustrates the problems that can arise in relation to these last two guidelines: Consider the improperly configured shield system shown in Figure 9, in which a precision voltage source, V1, and a digital logic gate share a common shield connection. This situation can occur in a large system where analog and digital signals are cabled together.

Figure 9. A situation that generates transient shield voltages.

A step voltage change in the output of the logic circuit couples capacitively to its shield, creating a current in the common 2-foot

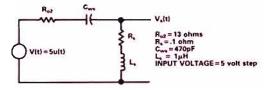

shield return. This, in turn, develops a shield voltage common to both the analog and digital shields. An equivalent circuit is shown in Figure 10, in which V(t) is a 5-volt step from a TTL logic gate,  $R_{\rm 0.2}$  is the 13-ohm output impedance of the logic gate,  $C_{\rm wx}$  is the 470-pF capacitance from the shield to the center conductor of the shielded cable, and  $R_{\rm s}$  and  $L_{\rm s}$  are the 0.1-ohm resistance and 1-microhenry inductance of the 2-foot wire connecting the shield to the system ground.

Figure 10. Equivalent circuit for generating shield voltage.

The shield voltage,  $V_s(t)$ , can be solved for by conventional circuitanalysis techniques, or simulated by actually building and carefully making measurements on a circuit with the given parameters. For the purpose of demonstration, the calculated response waveform, illustrated in Figure 11, with a 5-volt initial spike, resonant frequency of 7.3 MHz, and damping time constant of 0.15  $\mu$ s, is sufficient to illustrate the nature of the voltage that appears on the shield and is capacitively coupled to the analog input. If the voltage is looked at with a wideband oscilloscope, it will look like a noise "spike." We can see that this transient will couple a fast damped waveform of significant peak amplitude to the analog system input.

Figure 11. Computed response of circuit of Figure 10.

Even in a purely digital system, noise glitches can be caused to appear in apparently remote portions of a system having the kind of situation shown. This can often explain some otherwise inexplicable system bugs.

In quite a few cases, the proper choice of shield connection among the many possibilities may not be immediately obvious, and the guidelines may not provide us with a clear choice. There is no alternative but to analyze the various possibilities and choose the approach for which the lowest noise may be calculated.

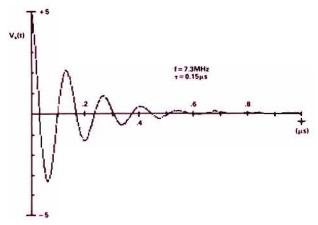

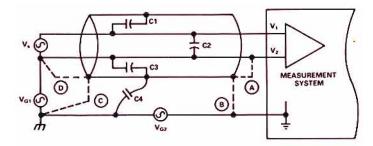

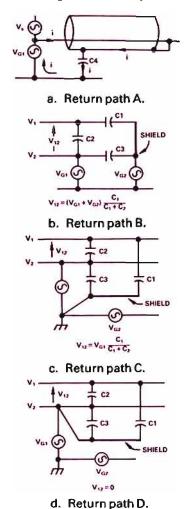

For example, consider the case illustrated in Figure 12, in which the measurement system and the source have differing ground potentials. Should we connect the shield to A: the low side at the measurement-system input, B: ground at the system input, C: ground at the signal source, or D: the low side at the source?

A is a poor choice, since noise current is allowed to flow in a signal

Figure 12. Possible grounds where system and source have differing ground potentials.

conductor. The path of the noise current due to  $V_{\rm GI}$ , as it returns through C4, is shown in Figure 13a.

B is also a poor choice, since the two noise sources in series,  $V_{G1}$  and  $V_{G2}$ , produce a component across the two signal wires, developed by the source impedance in parallel with  $C_2$ , in series with  $C_1$ , as shown in Figure 13b.

C is poor, too, since  $V_{G1}$  produces a voltage across the two signal wires, by the same mechanism as (B), as Figure 13c shows.

D is the best choice, under the given assumptions, as can be seen in Figure 13d. It also tends to confirm the grounding guideline to connect the shield at the signal's reference potential.

Figure 13. Equivalent circuits.

# NOISE RESULTING FROM A MAGNETIC FIELD

Noise in the form of a magnetic field induces voltage in a conductor or circuit; it is much more difficult to shield against than elec-

tric fields because it can penetrate conducting materials. A typical shield placed around a conductor and grounded at one end has little if any effect on the magnetically induced voltage in that conductor

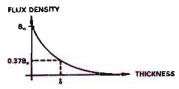

As a magnetic field, B, penetrates a shield, its amplitude decreases exponentially (Figure 14). The skin depth,  $\delta$ , of the shield material, is defined as the depth of penetration required for the field to be attenuated to 37% (exp (-1)) of its value in free air. Table 1¹ lists typical values of  $\delta$  for several materials at various frequencies. You can see that any of the materials will be more effective as a shield at high frequency, because  $\delta$  decreases with frequency, and that steel provides at least an order of magnitude more effective shielding at any frequency than copper or aluminum.

Figure 14. Magnetic field in a shield as a function of penetration depth.

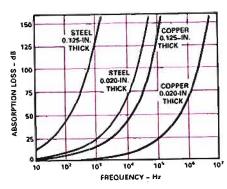

Figure 15 compares absorption loss as a function of frequency for two thicknesses of copper and steel. 1/8-inch steel becomes quite effective for frequencies above 200 Hz, and even a 20-mil (0.5 mm) thickness of copper is effective at frequencies above 1 MHz. However, all show a glaring weakness at lower frequencies, including 50-60-Hz line frequencies—the principal source of magnetically coupled noise at low frequency.

Figure 15. Absorption loss vs. frequency for two thicknesses of copper and steel.

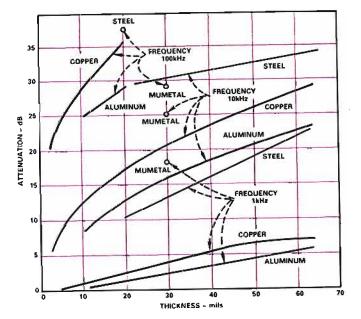

For improved low-frequency magnetic shielding, a shield consisting of a high-permeability magnetic material (e.g., Mumetal)

Table 1. Skin depth, 8, vs. frequency

|           | δ for C    | Оррег | δ for Al | uminum | 8 for Steel |       |  |  |

|-----------|------------|-------|----------|--------|-------------|-------|--|--|

| Frequency | (in.) (mm) |       | (in.)    | (mm)   | (in.)       | (mm)  |  |  |

| 60Hz      | 0.335      | 8.5   | 0.429    | 10.9   | 0.034       | 0.86  |  |  |

| 100Hz     | 0.260      | 6.6   | 0.333    | 8.5    | 0.026       | 0.66  |  |  |

| 1kHz      | 0.082      | 2.1   | 0.105    | 2.7    | 0.008       | 0.2   |  |  |

| 10kHz     | 0.026      | 0.66  | 0.033    | 0.84   | 0.003       | 0.08  |  |  |

| 100kHz    | 0.008      | 0.2   | 0.011    | 0.3    | 0.0008      | 0.02  |  |  |

| 1MH2      | 0.003      | 0.08  | 0.003    | 0.08   | 0.0003      | 0.008 |  |  |

Table 1 and Figures 15 and 16 are from Ott, H.W., Noise Reduction Techniques in Electronic Systems (New York: John Wiley & Sons, © 1976).

Figure 16. Shielding attenuation of Mumetal and other materials at several frequencies.

should be considered. Figure 16 compares a 30-mil thickness of Mumetal with various materials at several frequencies. It shows that, below 1 kHz, Mumetal is more effective than any of the other materials, while at 100kHz it is the least effective. However, Mumetal is not especially easy to apply, and if it is saturated by an excessively strong field, it will no longer provide an advantage.

As you can see, it is very difficult to shield against magnetic fields, i.e., to modify the coupling medium by shielding. Therefore, the most effective approaches at low frequency are to minimize the strength of the interfering magnetic field, minimize the receiver loop area, and minimize coupling by optimizing wiring geometries. Here are some guidelines:

- •Locate the receiving circuits as far as possible from the source of the magnetic field.

- Avoid running wires parallel to the magnetic field; instead, cross the magnetic field at right angles.

- •Shield the magnetic field with an appropriate material for the frequency and field strength.

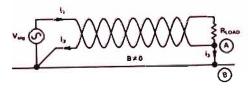

- •Use a twisted pair of wires for conductors carrying the high-level current that is the source of the magnetic field. If the currents in the two wires are equal and opposite, the net field in any direction

a. Correct connection with balanced currents.

b. Incorrect connection forming ground loop.

Figure 17. Connections to a twisted pair.

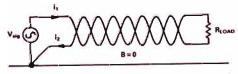

over each cycle of twist will be zero (Figure 17a). For this arrangement to work, none of the current can be shared with another conductor, for example, a ground plane. Figure 17b shows what can happen if a ground loop is formed; if part of the current flows through the ground plane (depending on the ratio of conductor resistance to ground resistance), it will form a loop with the twisted pair, generating a field determined by  $i_3$  (=  $i_1 - i_2$ ).

The ground connection between A and B need not be as simple as a short circuit to cause trouble. Any stray unbalanced capacitance or resistance from R<sub>load</sub> circuits to the ground plane will also unbalance the currents and produce a net current through the wires and the ground plane, producing a ground loop and a related magnetic field. For this reason, it is also good practice to run the twisted pair close to the ground plane to tend to balance the capacitances from each side to ground, as well as to minimize loop area.

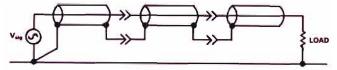

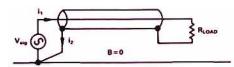

•Use a shielded cable with the high-level source circuit's return current carried in the shield (Figure 18). If the shield current, I<sub>2</sub> is equal and opposite to that in the center conductor, the center-conductor field and the shield field will cancel, producing a zero net field. In this case, which seems to violate the "no shield current" rule for receiver circuits, the concentric cable is not used to shield the center lead; instead, the geometry produces cancellation.

Figure 18. Use of shield for return current to noisy source.

This scheme can be usefully employed in an ATE system where accurate measurements must be performed on devices with high power-supply currents that may be noisy. For example, Figure 19 shows the application of this technique to the connections for the high-current logic supply for an a/d converter under test—at the end of a test cable.

Figure 19. Application of circuit of Figure 18 in a test system.

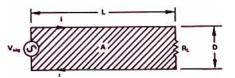

•Since magnetically induced noise depends on the area of the receiver loop, the induced voltage due to magnetic coupling can be reduced by reducing the loop's area. What is the receiver loop? In the example shown in Figure 20, the signal source and its load are connected by a pair of conductors of length L and separation D. The circuit (assuming it has a rectangular configuration) forms a loop with area D·L.

Figure 20. Area of a loop that receives magnetically coupled noise.

The voltage induced in series with the loop is proportional to the area and the cosine of its angle to the field. Thus, to minimize noise, the loop should be oriented at right angles to the field, and its area should be minimized.

The area can be reduced by decreasing the length of and/or decreasing the distance between the conductors. This is easily accomplished with a twisted pair, or at least a tightly cabled pair, of conductors. It is good practice to pair conductors so that the circuit wire and its return path will always be together. To do this, the designer must be certain of the actual path that the return current takes in getting back to the signal source. Quite often, the current returns by a path not intended in the original design layout.

If wires are moved (for example, by a technician troubleshooting some other problem), the loop area and orientation to the field may change, so that yesterday's acceptable noise level may be transformed to tomorrow's disastrous noise level. Which may lead to a service call... and another repetition of the cycle. The bottom line: Know the loop area and orientation, do what must be done to minimize noise—and permanently secure the wiring!

## **DRIVEN SHIELDS AND GUARDING**

We have discussed the role of a current-driven shield carrying an equal and opposite current to reduce generated noise by reducing the magnetic field around a conductor.

Guarding is similar, in that it involves driving a shield, at low impedance, with a potential essentially equal to the common-mode voltage on the signal wire contained within the shield. Guarding has many useful purposes: It reduces common-mode capacitance, improves common-mode rejection, and eliminates leakage currents in high-impedance measurement circuits.

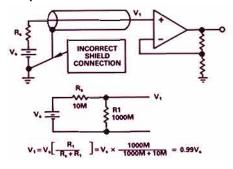

Figure 21 shows an example of an op amp with negligible bias current connected as a high-impedance non-inverting amplifier with gain. The purpose of the cable is to shield the high input-impedance signal conductor from capacitively coupled noise and to minimize leakage currents. The signal comes from a 10-megohm source, and the cable is assumed to have 1000 megohms of leakage resistance (which may change as a function of temperature, humidity, etc.) from conductor to shield. If connected as shown, the equivalent input circuit is an attenuator which loses 1% of the

Figure 21. Op amp connected as high-impedance non-inverting amplifier with gain, with shielded input lead.

signal at the time it is measured, and an unknown fraction at other times. Also, the cable capacitance produces a substantial lag time constant, R<sub>s</sub>C<sub>c</sub>.

Figure 22 has the same players, but the shield is connected to the tap of the gain divider (usually at low impedance). Being connected to the inverting input of the op amp, it should be at the same potential as the amplifier's non-inverting input. Since there is no voltage across the cable's leakage resistance, there is no current through it and its resistance value doesn't matter;  $V_1$  must therefore be equal to  $V_{ss}$  since bias current was assumed negligible.

Figure 22. Same as Figure 21, but cable shield connected as a guard.

Also, there is no voltage across the cable capacitance, hence no charging or discharging of the cable; thus the lag time constant depends mainly on circuit strays and the amplifier's input capacitance. For stability, capacitance should be connected between the output and the negative input, such that  $C_f R_F = C_s R_i$ , where  $C_s$  is sum of the stray capacitance between shield and ground and the input capacitance.

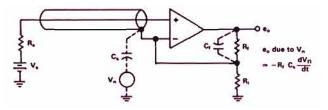

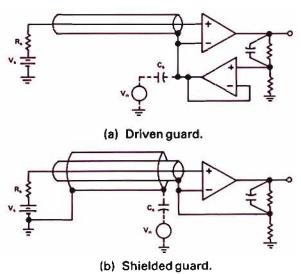

There must be no noise voltage applied to the guard. In noisy systems, as Figure 22 shows, capacitively coupled noise will be differentiated, emphasizing the higher-frequency components. This can be avoided (Figure 23) by either using a buffer follower with fast response and low output impedance to drive the guard (a) or a second shield, around the guard, grounded to the signal common (b).

Figure 23. Avoiding noise pickup on the guard.

In high-impedance current-input inverting configurations, where a length of shielded wire is used to guard the lead from the current source to the amplifier's inverting input, the guard should either be driven by a buffer at the same potential as the non-inverting input (and connected nowhere else), or be tied directly to the non-

inverting input, with a second outer shield connected to the signal's reference point.

#### SUMMARY

Table 2 summarizes the important points made in this article. All are important to maintaining a high-integrity shield system. However, we cannot emphasize too strongly the two subjects that are most-often ignored: appearance of noise voltage on signal shields and proper disposition of shield noise currents. Noise voltage must not exist on the shield; shield-to-conductor capacitance will couple the noise directly to the center conductor. If shield currents are not returned properly, they can show up in a remote part of the system and perhaps cause trouble in a location totally unrelated to the shielding problem that was "solved."

Table 2. Applicability of shielding considerations

| Consideration                                                                              | Universal | Electric | Magnetic |

|--------------------------------------------------------------------------------------------|-----------|----------|----------|

| Know the noise source, coupling medium, and receiver.                                      | x         | x        | x        |

| Different shielding techniques are required for different noise sources, coupling channels | i.        |          |          |

| and receivers.                                                                             | ' x       | Х        | X        |

| In most situations, conventional circuit                                                   |           |          |          |

| analysis using lumped elements can be used.                                                | Х         | Х        | X        |

| Connect the shield at the signal-source end                                                |           | v        |          |

| only.                                                                                      |           | X<br>X   |          |

| Carry shields through connectors.                                                          |           | X        |          |

| Individual shields should not be tied together                                             | •         | x        |          |

| Do πot ground both ends of a shield.  Do not allow shield current to flow,                 |           | ^        |          |

| except for driven shields - to cancel                                                      |           |          |          |

| magnetic fields                                                                            |           | х        | х        |

| Do not allow voltage on a shield, except                                                   |           |          |          |

| for guarding.                                                                              |           | Х        |          |

| Know exactly where noise current                                                           |           |          |          |

| from the shield will flow.                                                                 |           | X        |          |

| Use short connections to return noise                                                      |           |          |          |

| current from the shield.                                                                   |           | X        |          |

| Electrostatic shields have little effect in reduc                                          | -         |          |          |

| ing noise resulting from magnetic fields.                                                  |           |          | X        |

| Reduce magnetic fields by physical separa-                                                 |           |          |          |

| tion proper orientation, twisted pairs, and/or                                             | •         |          |          |

| driven shields.                                                                            |           |          | X        |

| Know the receiver loop area and orientation                                                |           |          |          |

| to the field. Keep field at right angles and                                               |           |          |          |

| reduce the loop area by using paired                                                       |           |          |          |

| conductors, preferably twisted pairs, and                                                  |           |          | x        |

| minimize wire lengths.                                                                     | x         | x        | ^        |

| Use guarding in high-impedance circuits                                                    | ^         | ^        |          |

| In high-impedance circuits, be extremely careful of shield noise                           | x         | х        |          |

| Caretal of silicid horse                                                                   | ^         | ^        |          |

#### **BRIEF BIBLIOGRAPHY**

For further reading, see:

Brokaw, A. Paul. "Analog Signal Handling for High Speed and Accuracy," Analog Dialogue 11-2, 1977, pp. 10-16.

Brokaw, A. Paul. "An I.C. Amplifier Users' Guide to Decoupling, Grounding, and Making Things Go Right for a Change," *Analog Devices Data-Acquisition Databook* 1982, Volume I, Pages 21-13 to 21-20.

Morrison, Ralph. Grounding and Shielding Techniques in Instrumentation Second Edition. (New York: John Wiley & Sons, 1977).

Ott, Henry W. Noise Reduction Technique in Electronic Systems. (New York: John Wiley & Sons, 1976).

Analog Dialogue 17-1 1983

# FAST, FLEXIBLE SWITCHED DUAL-INPUT OP AMP & COMPARATOR

# Use This IC as a Modulator/Demodulator, Lock-In Amplifier, Phase Detector Synchronous Detector, Rectifier, Dual-Mode Circuit, ...And Much More

by Paul Brokaw, Moshe Gerstenhaber, and Steve Miller

Model AD630\* is an unusual new low-cost, single-chip, precision analog IC that can be used for the above functions with little or no additional circuitry. As a lock-in amplifier, it can recover a 0.1 Hz sine wave, transmitted as a modulation on a 400-Hz carrier, from a band-limited, clipped white-noise signal approximately 100,000 times larger—a dynamic range greater than 100 dB.

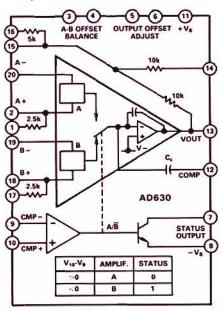

#### **FUNCTIONAL ARCHITECTURE**

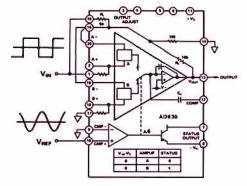

The stylized block diagram of Figure 1 shows the essential circuit elements of the AD630. Despite the formidable appearance of its array of 20 terminals, which make possible a wide range of applications, the basic idea behind the AD630 is rather simple. It consists of a frequency-compensated op-amp output stage with two identical switched differential front ends (A and B), a differential comparator that controls the switching (CMP), and a set of jumper-programmable matched precision resistors—trimmed to produce closed-loop gain accuracies to  $\pm 0.05\%$  and gain match (between channels) to  $\pm 0.03\%$ .

Figure 1. Functional diagram of the AD630.

When the input to the comparator's non-inverting input (CMP+) is more positive (or less negative) than the inverting input (CMP-), front-end A will be selected; when CMP+ is less positive than CMP-, B is selected. A status output, available via an open-collector transistor, indicates the comparator's state.

Suppose B is selected. The inputs labeled B + and B - are the non-inverting and inverting inputs of an op amp, with output terminal at VOUT. It will behave just like an op amp with open-loop gain of 100 dB min, small-signal bandwidth of 2 MHz, and slew rate of 35 V/ $\mu$ s, and will perform the many functions op amps are used

\*Use the reply card for technical data and applications information.

See 1982 IEEE International Solid-State Circuits Conference Digest of Technical Papers, p.44.

for. Offset voltage is  $\pm 100\mu V$  max (AD630B), drift is  $1 \mu V/^{\circ}C$  typically, and input bias/offset currents are 100/10 nA. The precision resistors provided on-chip can be used for accurate inverting and non-inverting gains of -1, -2, -3, and +1, +2, +3, and +4 V/V, without any external resistors. Other channel gains and op-amp circuits can be configured using external components.

Similarly, when A is selected, the device will behave like an op amp, with non-inverting input at A +, inverting input at A -, output at VOUT, and the same specs as for B. The same set of resistors can be used for circuits involving both A and B, because the unengaged front end's impedance remains high when it is deselected.

This flexibility permits the device to function in a wide variety of applications. It can produce dual-mode operation with differing magnitudes and polarities of gain for a single input, or it can multiplex two inputs with differing gains and polarities. Because the comparator can be driven by either a digital signal or an analog signal of sufficient magnitude, the device can also be used recursively, with the output affecting the state of the comparator.

### **HOW IT IS USED**

The device may be used as a phase-sensitive detector with gain of 2, for a modulated signal voltage, by comparing the signal's phase with that of a control voltage at the same frequency as the carrier. When the control voltage  $(V_{CMP} + V_{CMP})$  is positive, the gain is positive, and when the control voltage is negative, the gain is negative. Thus, the output will be positive when the signal is in phase with the control voltage, negative when the signal is 180° out of phase, and zero-average when the signals are in quadrature (Figure 2).

Figure 2. Waveforms at quadrature in a synchronous detector.

Figure 3 shows a scheme for operation in this mode. When the control voltage, applied to the comparator, is positive, Channel A is selected; for negative control voltage, Channel B is selected. Channel A has a gain of +2, and Channel B has a gain of -2.

As Figure 3 shows, the input is applied to the non-inverting input of A, via the internal  $2.5 \,\mathrm{k}\Omega$  bias-current-compensation resistor, at pin 1, and also to the inverting input of B, via a  $5 \,\mathrm{k}\Omega$  input resistor, at pin 16. The inverting inputs of A and B are connected together, and to the tap of the  $10 \,\mathrm{k}\Omega$  feedback divider, but only one front end is working at any given time.

Figure 3. AD630 applied as a synchronous detector.

To understand how it works, we will consider ideal cases; actual operation is not greatly dissimilar. When A is selected, the feedback to A – must be almost exactly equal to the voltage at A +. In the ideal case, no current flows to B –, no current flows in the 5-k $\Omega$  resistor (since  $V_{A-} = V_{IN}$ ), and no current flows to A –; therefore  $V_{A-} = V_{OUT}/2$ , hence  $V_{OUT} = 2 V_{A-}$ .

When B is selected, the device looks like an inverting op amp, programmed for a gain of -2, with  $R_i=5~k\Omega$ ,  $R_f=10~k\Omega$ , and a  $10\text{-}k\Omega$  load to ground at the summing point:  $R_f/R_i=10~k\Omega/5~k\Omega$ . Since the voltages at both ends of the grounded resistor are zero, no current flows, and its loading effect is negligible.

Although A – and B – are connected together, there is little or no interaction, since both front ends are always at high impedance, even when they are disengaged from the device's output stage. However, the load seen by the external input  $(V_{IN})$  can change (for example, in this case, it is  $5k\Omega$  when B is selected and at very high impedance for A); therefore, the signal driving point should be at low dynamic impedance, to avoid intermodulation effects.

The device is housed in a 20-pin DIP, and it has a supply voltage range of  $\pm 16.5$ V to  $\pm 5$ V, with 4-mA typical quiescent current drain. With  $\pm 15$ -volt supplies, its input common-mode range is  $\pm 10$ V (CMR = 90 dB min – B version), and the specified minimum output range is  $\pm 10$ V into a 2-k $\Omega$  load; power-supply rejection is 90 dB min. Settling time is 3 $\mu$ s to 0.01% for a 20-volt step, and channel separation at 10 kHz is 100 dB. It is available in two – 25°C-to-+85°C grades (AD630A and AD630B), differentiated principally by offset, drift, gain error and mismatch, and the AD630S for –55°C to +125°C. Prices (100s) are \$9.95/\$14.95/\$18.95 for A/B/S.

### **APPLICATIONS**

The AD630 was intended for wideband, low-level, and wide dynamic-range instrumentation applications. It is capable of such analog signal-processing functions as balanced modulator, balanced demodulator, absolute-value amplifier, phase detector, square-wave multiplier, and two-channel precision multiplexer.

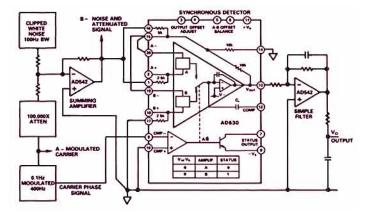

Figure 4 is the schematic diagram of a circuit to demonstrate the dynamic range of an AD630 as it might be used in a lock-in amplifier. Lock-in techniques are frequently used to separate a small narrow-band signal from interfering noise. The lock-in amplifier serves as both narrow-band filter and detector.<sup>2</sup> When the frequency and phase of the signal are known, very small signals

Figure 4. Lock-in amplifier circuit.

can be detected in the presence of large amounts of uncorrelated noise.

The lock-in amplifier is basically a synchronous demodulator, followed by a low-pass filter. An important measure of performance is the dynamic range of its demodulator. Figure 5 shows the recovery of a signal modulated at 400 Hz from a noise signal approximately 100,000 times larger, a dynamic range of 100dB.

Figure 5. Waveforms for lock-in amplifier (see text).

The test signal is produced by modulating a 400-Hz carrier with a 0.1-Hz sine wave. The signals that are produced by chopped radiation detectors (infra-red, optical, etc.) may have similar components; a sine wave is used for clarity of illustration. This signal, present at point "A" of Figure 4, is shown by the upper trace of Figure 5. It is attenuated 100,000 times, normalized to the output "B" of the summing amplifier. A band-limited clipped white-noise signal, which might represent, for example, background and detector noise in the chopped radiation case, is added to the modulated signal by the summing amplifier. Figure 5's center trace shows the sum of signal and noise at point B.

The combined signal is demodulated synchronously, using phase information derived from the modulator, and the result is low-pass filtered using a simple 2-pole filter with a dc scaling gain of 100. This recovered signal is the lowest trace of Figure 5.

The combined signal contrived for this illustration is similar to the signals often requiring a lock-in amplifier for detection. The precision input performance of the AD630 provides more than 100 dB of signal range, and its dynamic response permits it to be used with carrier frequencies more than two orders of magnitude higher than that used in this example. A more-sophisticated low-pass filter will aid in rejecting wider-bandwidth interference.

Incidentally, an AD630 was also used as the modulator for the circuit of Figure 4. These examples illustrate the power of the AD630 in just one of its applications. A general-purpose device, its many latent uses challenge the creativity of the potential user.

15

<sup>&</sup>lt;sup>2</sup>See "Lock-In Amplifier Uses Single IC," Analog Dialogue 8-1 (1974), for an example of a lock-in amplifier employing a differential instrumentation amplifier and external active and passive components.

# LEVEL-INDEPENDENT AUTOMATIC GAIN CONTRÛL

# LOGDAC<sup>TM</sup> Controls Output Signal Amplitude Over Wide Range of Input AD7111 Resolves to 0.375 dB, Provides Digital Readout of Input Level

by John Wynne

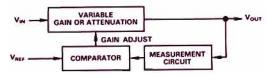

Figure 1 shows the essential components of a basic automatic gaincontrol (AGC) loop: the dc reference signal, V<sub>REF</sub>, establishes the output amplitude set-point; the output-measurement circuit obtains a running measure of the output level, based on a property (peak, average, rms, etc.) of the output signal; a comparator, derives a control signal; and a gain-adjustment circuit, applies enough distortionless gain or attenuation to the input signal to maintain the output level sufficiently close to the reference value.

Figure 1. Automatic-gain-control loop.

The circuit examples shown here were designed to control output amplitudes for more than 40 dB of input range, for signal frequencies to beyond 20 kHz. Two cases are shown: in one, the input signal arrives at a higher level than the required output and must be attenuated; in the other, a low-level signal requires gain.

# **AGC WITH LOGDACS**

The LOGDAC<sup>TM</sup> is a class of multiplying digital-to-analog converter that accepts bipolar analog input signals and provides an exponential (antilog) relationship between the digital input and the analog gain (or attenuation). For example, the AD7111\* has an 8-bit µP-compatible digital input, with resolution of 0.375 dB per bit and a dynamic range of up to 88.5 dB of attenuation.

Among their many applications, logarithmic DACs are useful in automatic level control applications employing multiplying DACs. The salient features that make them desirable include their wide dynamic range and their equal-percentage-per-bit gain change. For example, when the input code of a linear 8-bit DAC changes by 1 bit near full scale, the fractional gain change is of the order of ½50, and when the code changes by 1 bit near zero, the percentage gain change is of the order of 100%; on the other hand, the nominal gain change of an AD7111 over the active range of digital input is a fixed 0.375 dB—or 4.4% of reading—per bit.

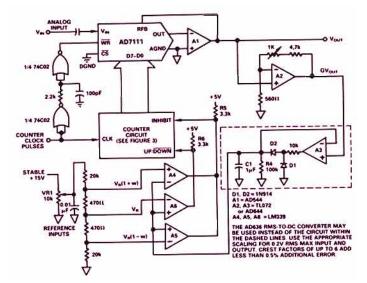

In Figure 2, an AD7111 controls the attenuation for applications in which the input is at a high level compared to the output. With op amp A1, the regulator output amplifier, the AD7111 produces whatever attenuation of the analog signal input is required to maintain the output level. The digital input is increased or decreased, one 0.375-dB step at a time, by an 8-bit up/down counter. The counter, pulsed by a clock, is driven in the appropriate direction by the output of a comparator, A6, which compares the reference voltage with an amplified (A2), peak-rectified (A3) version of the measured output voltage. The window comparator, A4 & A5, provides hysteresis, so that counting is inhibited when the output level is within a defined range of values.

Figure 2. AGC loop using AD7111 for attenuation.

For the application shown here, the nominal output level is about 100 mV peak-to-peak. A2 provides amplification of the signal, about 10X, before it is peak-rectified. The reason for amplification is that the ripple content of the peak-detector output is not a constant percentage of signal amplitude—lower signal levels are accompanied by higher percentage ripple, which can lead to poor regulation when the input to the rectifier is well below 0.5V peak. VREF should be scaled by the same amount as the closed-loop gain of A2. Thus, if A2's closed-loop gain is 10, VREF should be 0.5V for a 50-mV peak output level. The input should be either accoupled, as shown, or symmetric about zero, to avoid the possibility of an input bias driving the peak-follower negative.

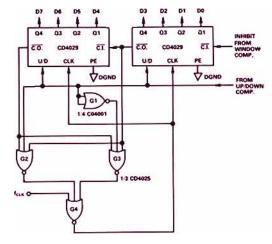

The output of the peak follower is compared with  $V_{REF}$  in A6, and with  $V_{REF}(1+W)$  and  $V_{REF}(1-W)$  in A4 and A5. The counter (Figure 3) will count down if the rectified voltage is less than  $V_{REF}$ , decreasing the AD7111's attenuation—and up if greater, to increase attenuation. If the rectified voltage is within about  $\pm W$  of

Figure 3. Counter circuit for Figures 1 and 4.

<sup>\*</sup>Use the reply card for technical data.

<sup>†</sup>RMS could also be employed, with excellent results, using the AD636 RMS-to-

V<sub>REF</sub>, the count will be inhibited, in order to provide sufficient hysteresis to avoid a ± 1-bit high-frequency "hunting" of the amplitude. In this example, W is about 2.3%.

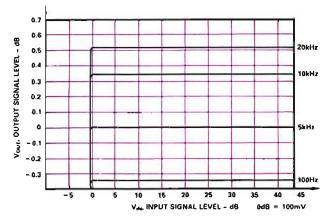

Figure 4 is a plot of response at selected frequencies from 100 Hz to 20 kHz for a sine wave input from 0 dB to +40 dB, relative to the output level, which corresponds to 100 mV peak-to-peak. Note the flat response over the whole range of amplitudes. There is some variation with frequency (not a problem at fixed carrier frequencies) due to the rectifier's dynamic response characteristics.

Figure 4. Response characteristics of circuit of Figure 2.

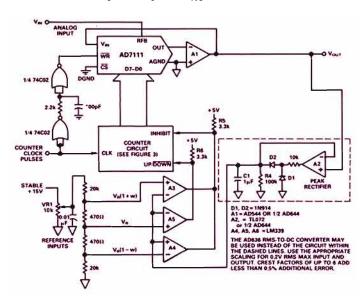

Figure 5 shows the corresponding circuit employed for applications in which the input is low and must be amplified to reach the desired output level. The AD7111 is connected to attenuate the feedback around A1, thus providing overall gain. An increasing digital input to the AD7111 will cause the feedback attenuation to increase, thus increasing the overall gain in 0.375-dB-per-bit steps. Since the output level is sufficiently high for good results with the peak detector, the scaling amplifier (A2 in Figure 1) is omitted. Thus, for 6.5 volts peak-to-peak,  $V_{REF}$  is 3.25 V.

Figure 5. AGC loop using AD7111 for gain.

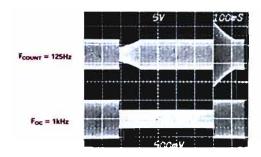

The response of this circuit, for an input sine wave of amplitude from 0 to -40 dB, referred to the output, is similar to that shown in Figure 4. Figure 6 shows the transient response of the circuit of Figure 5 to + and - 6-dB steps (50% amplitude changes) of a 1-kHz input signal. Settling occurs within about 130 milliseconds, using a 125-Hz clock frequency for the counter circuit. (At 125 Hz,

the pulse period is 8 ms, and at 0.375 dB per step, 16 steps are required to reach 6 dB. The count stops when the *inhibit* band is reached.)

The response of the system is determined by the relation between the frequency of the clock used for the up/down counter and the lowest expected fundamental signal frequency. The lower that signal frequency, the longer the filter discharge time-constant must be, in order for the ripple to be kept within the comparator window between signal peaks. Then, if the clock frequency is too high, a step increase in the signal level will result in an undershoot of the regulated response. The reason? Although the output responds immediately to the input and the gain control, the peak-follower output that is fed back responds quickly to increases but decays slowly on decreases—one or more additional clock cycles may occur before the reference level is reached, temporarily allowing the actual amplitude to be brought below its final value. A useful rule of thumb: establish a clock frequency from 1× to 2× the lowest signal frequency.

If the input can be both larger and smaller than the output, the regulating circuit must be able to provide both amplification and attenuation. This is achieved by increasing the gain of A2 in Figure 1 by an amount equal to the lowest value of the minimum signal level (in dB, referred to the output). For example, if the input signal is expected to swing from -10 dB to +20 dB, referred to the output, then the gain of A2 should be increased by 10 dB to insure that the AGC loop is active over the entire input signal swing.

#### A/D CONVERSION

While performing their AGC function, these circuits also act as tracking analog-to-digital converters, since the varying digital code present at the counter output (AD7111 input) represents a logarithmic measure of the ratio between the analog input and output levels (i.e., the attenuation or gain required for correction). This output may be used for any digital purpose (storage, computation, etc.) or for driving slaved AD7111s to set gains elsewhere in the system in proportion to changes in the analog input.

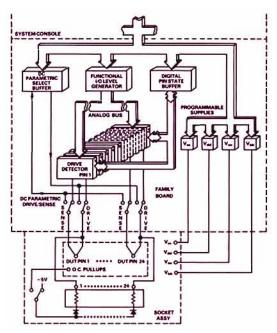

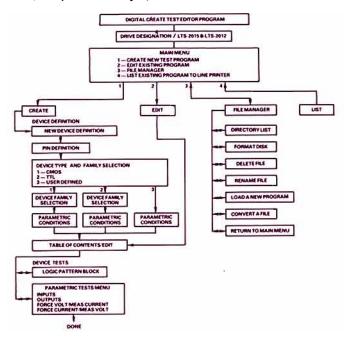

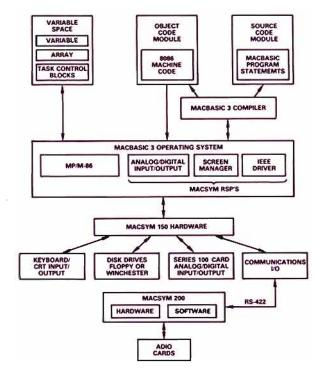

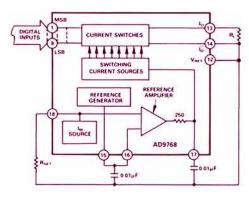

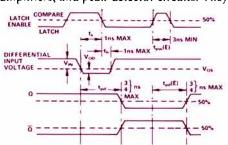

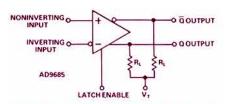

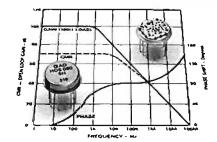

Since the AD7111 has on-chip registers, the digital code can be latched, freezing the gain of the system. This can be vital in applications where the input signal may disappear altogether, e.g., due to excessive fading or an interruption in the signal path. In many AGC systems, when this happens, the gain of the loop will increase to maximum, which can result in system oscillation when the input signal is restored. The digital control word (Figure 1 or Figure 4) can be frozen by bringing  $\overline{CS}$  (Chip Select) high. In such applications,  $\overline{CS}$  can be driven by a suitable input signal detector, set to detect out-of-range input signals.